学到了(分析集成稳压器的稳压性能)线性集成稳压器调整管工作在,通过高带宽集成稳压器增强输电网络,带宽,

随着技术的进步,处理器和其他高速数字组件(如 CPU、GPU、ASIC 和 FPGA)需要越来越高的功率,这意味着稳压器需要能够动态地向负载提供电流。较低的电压要求、高电流和更快的瞬变以及更严格的电压窗口导致更加强调将电流传输到处理器的 PCB 走线的性能。

本文引用地址:

稳压器和负载之间的输电网络 (PDN) 极大地影响了稳压器的电流源能力。PDN 是无源元件(通常是电容器)和将稳压器输出连接到负载输入的路由(金属层和过孔)的组合。它可以由寄生电阻、电容和电感元件的电路表示。

与传统稳压器相比,高带宽集成稳压器 (IVR) 可以放置在更靠近处理器的位置,从而简化 PDN 并允许更多快速响应动态负载要求的能力。IVR 使用户能够将稳压器放置在处理器下方,从而简化 PDN 并减少走线电阻的功率损耗。

垂直供电提高了负载的供电性能。它还允许更少的 PCB 层数和 PCB 顶部为其他元件提供更多空间,从而降低了 PCB 的复杂性。IVR 的主要区别在于,它们将输入和输出电容器集成到芯片中,以进一步减少 PCB 上的元件数量。高频开关增加了带宽,并进一步减少了对输出电容器的需求。此外,它还提高了负载瞬态性能,并允许更平坦的输出阻抗曲线。

PCB 阻抗和 PDN 目标阻抗挑战

在 CPU、GPU 和 FPGA 等现代高性能应用中,在满足其功耗要求的同时为负载供电的能力变得越来越重要。正确的 PCB 设计也是如此,以确保可以满足负载的功率要求。

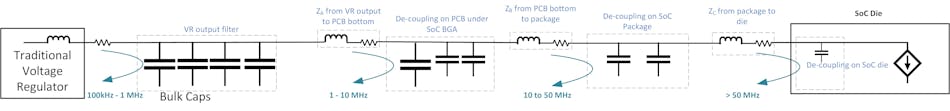

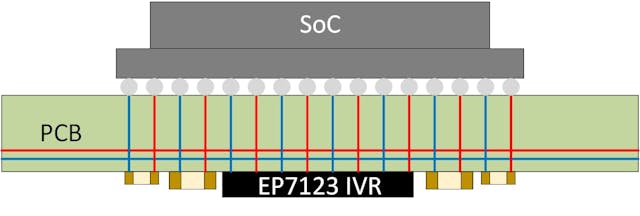

稳压器和负载之间的 PDN 对稳压器的源电流能力有很大影响。PDN 由用于将稳压器输出连接到 SoC 负载的电容器、PCB 走线、层和通孔组成(图 1)

图1. 传统稳压器和 SoC 负载之间的 PDN 示例。

图1. 传统稳压器和 SoC 负载之间的 PDN 示例。PDN 的寄生电阻增加了电源电路的功率损耗,从而降低了系统效率,并导致稳压器和负载之间的电压降。较大的寄生电阻要求稳压器调节更高的输出电压,以满足负载的电压要求。这会导致更大的功率损耗;因此,必须最小化 PDN 中的寄生电阻。PDN 中较大的电感会阻止稳压器提供高频负载瞬变。

PDN 必须满足目标阻抗,才能使稳压器在不违反任何功率要求的情况下为负载供电。由于负载瞬变而导致的 PDN 上的电压下降可由以下公式确定:

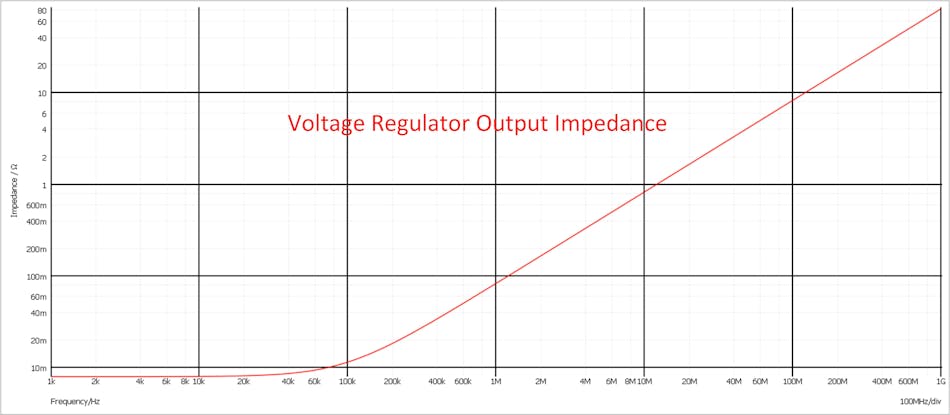

保持较小的 ZPDN 还允许用户将其稳压器的输出电压编程为较低的值,从而节省系统功耗。通过仔细设计 PCB,可以降低 ZPDN。PCB 走线的阻抗与其寄生电感成正比,与其寄生电容成反比。

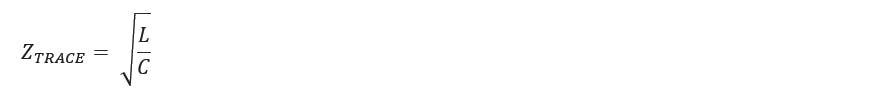

为了降低 PDN 阻抗,稳压器的输出端通常需要一个大型电容器组,并在 SoC 下方安装去耦电容器。电容器组增加的电容增加了上述方程的分母,从而降低了整体阻抗。SoC 下方的电容器组要求将稳压器放置在 SoC 的侧面,这意味着电流必须横向移动,从而增加寄生电感和电阻(图 2)。

图2. 这种传统的稳压器通过 PCB 横向为 SoC 负载供电

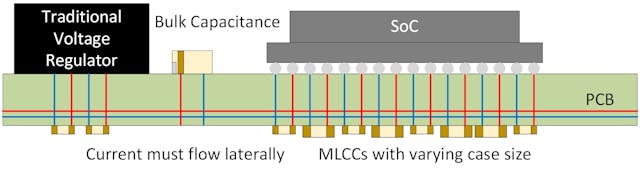

图2. 这种传统的稳压器通过 PCB 横向为 SoC 负载供电稳压器的输出阻抗可以用一个与电感器串联的电阻器来表示。电阻器代表输出负载调整率。电感代表稳压器的带宽,因此代表稳压器对瞬态负载条件的响应能力。通常,等效电感比功率级电感低大约一个数量级,功率级电感是根据电路的开关频率、输入电压、输出电压和所需的电感电流纹波来选择的。图 3 显示了标准 DC-DC 降压转换器的输出阻抗。

图3. 标准降压转换器的输出阻抗可以用一个与电感串联的电阻器来表示。

图3. 标准降压转换器的输出阻抗可以用一个与电感串联的电阻器来表示。电容器可用于补偿稳压器的等效电感,从而在较宽的频率范围内产生平坦的阻抗。

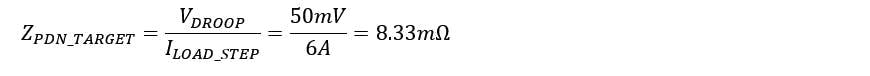

要确定设计必须针对的阻抗规格,工程师必须知道其最大负载阶跃和允许的电压下降。例如,如果工程师的最大负载阶跃为 6 A,最大电压偏差为 50 mV,则目标阻抗可使用以下公式计算:

开关频率为 1 MHz 的标准稳压器的带宽为 100 kHz,瞬态响应时间为 1 μs。使用这个控制环路带宽和上述目标 PDN 阻抗,我们传统稳压器的输出电感必须为:

工作频率为 1 MHz 且主电感器为 200 至 500 nH 的标准开关稳压器是实现此输出电感的合适选择。为了补偿稳压器的输出电感以尽可能保持阻抗平坦,必须使用电感较低 (ESL) 的电容器,其中电容为 C1 > C2 > C3,ESLC1 > ESLC2 > ESLC3。

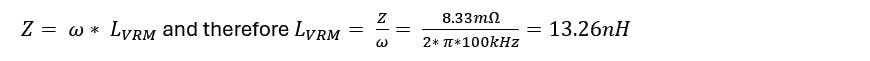

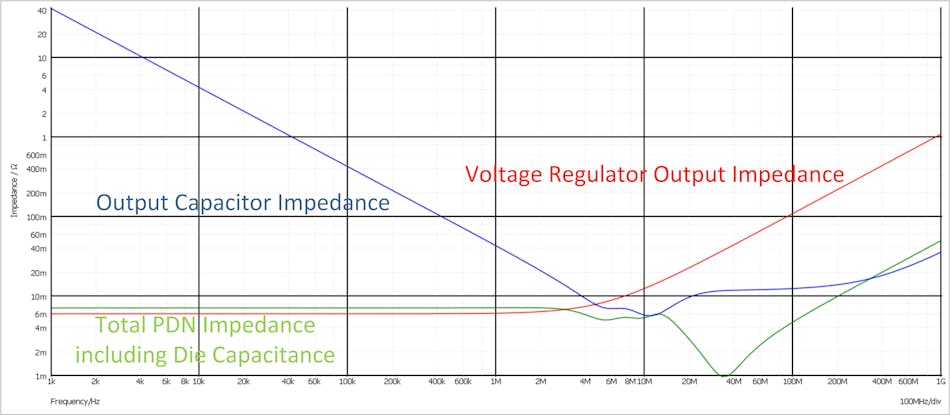

陶瓷电容器的 ESL 通常与其外壳尺寸成正比。选择不同外壳尺寸的多个不同电容器,使工程师能够在更宽的频率范围内创建平坦的阻抗。本示例使用一个 180 μF 大容量电容器、2 个 100 μF 0805 陶瓷电容器、2 个 47 μF 0603 陶瓷电容器、1 个 10 μF 0402 陶瓷电容器、2 个 2.2 μF 0402 陶瓷电容器、1 个 1.0 μF 0201 陶瓷电容器和 3 个 EC1001 200 nF 硅电容器。利用这些电容值可以得到图 4 所示的阻抗曲线,它满足了高达 168 MHz 的目标阻抗。

图4. 稳压器的 PDN 阻抗可以用不同外壳尺寸和值的电容器进行补偿,以创建一个在很宽的频率范围内满足我们目标的阻抗曲线。

图4. 稳压器的 PDN 阻抗可以用不同外壳尺寸和值的电容器进行补偿,以创建一个在很宽的频率范围内满足我们目标的阻抗曲线。高频 IVR 带来的 PDN 改进

IVR 是一种稳压器,它利用小工艺几何、高开关频率和更高的集成度,使稳压器尽可能靠近负载。一般来说,IVR 的开关频率是传统 DC-DC 稳压器的 100 倍,通常在 10 到 100 MHz 范围内。

以更高的开关频率工作会增加稳压器的环路带宽,并减少对大型电容器组的需求,以满足瞬态要求。此外,IVR 通常使用多相来进一步增加环路带宽并降低输出电容要求。

IVR 的一个例子是 Empower Semiconductor 的 EP7123,它使用四相提供 6 A 的电流,带宽约为 8 MHz。为了实现上述目标 PDN 阻抗,IVR 输出电感必须如下:

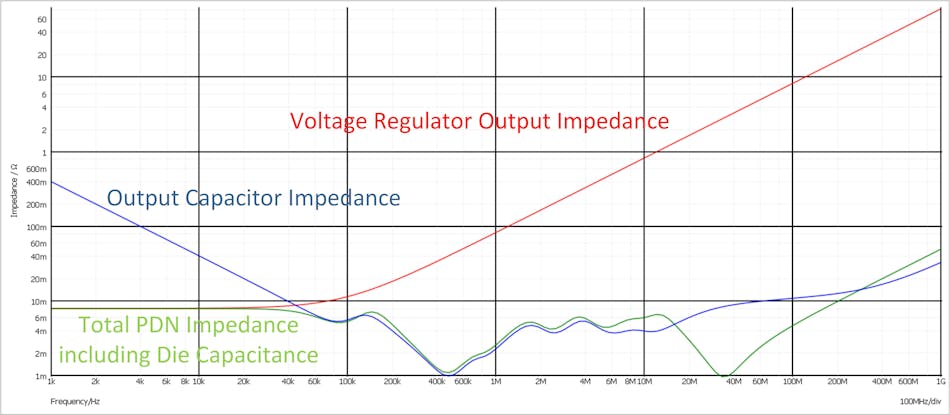

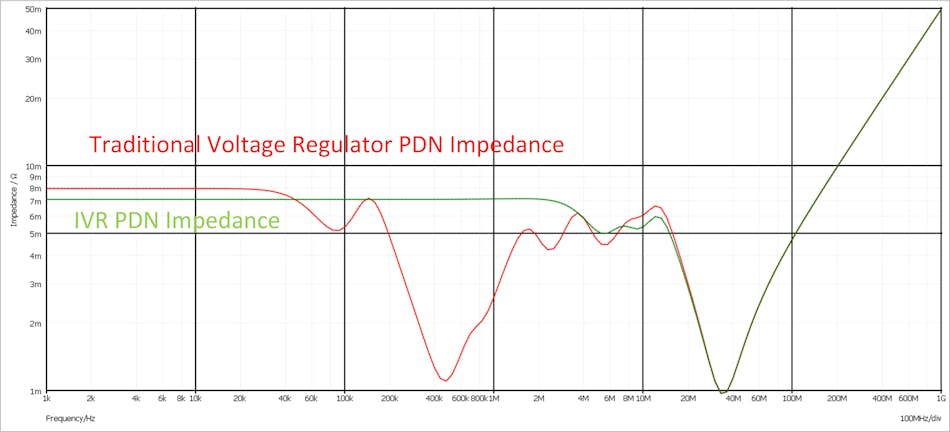

这比传统稳压器的等效输出电感小 100 倍。图 5 描述了前面显示的传统稳压器与多相 IVR 的输出阻抗比较。

这比传统稳压器的等效输出电感小 100 倍。图 5 描述了前面显示的传统稳压器与多相 IVR 的输出阻抗比较。 图5. IVR 的输出电感比传统稳压器低几个数量级,从而在更宽的频率范围内实现平坦的阻抗曲线。

图5. IVR 的输出电感比传统稳压器低几个数量级,从而在更宽的频率范围内实现平坦的阻抗曲线。阻抗图表明,IVR 的输出电感比传统的稳压器低得多,这会导致阻抗开始以更高的频率上升。对 IVR 使用多相使输出电感并联并联,并进一步降低阻抗。多相 IVR 的较低输出阻抗使设计人员能够减少放置在 PDN 中的电容器数量,以满足目标阻抗。

这些差异显著缩短了稳压器的响应时间。标准开关稳压器的带宽约为 100 kHz,响应时间为 10 μs。相比之下,多相 IVR 的带宽可以超过 10 MHz,响应时间为 100 ns。

IVR 还可以实现低于 0.8 mm 的解决方案高度,这远低于传统的稳压器解决方案。较低的解决方案高度允许将 IVR 放置在 PCB 的背面,负载的正下方(图 6)。

6. IVR 可以放置在 SoC 的正下方,以实现垂直供电。

启用垂直供电简化了从 IVR 到负载的 PDN,从而降低了供电路径的阻抗。最重要的是,EP7123 集成了输出电容器,减少了将这些组件放置在外部的需要。所有这些都降低了整体阻抗、对大容量电容器的需求以及由于走线电阻引起的功率损耗。

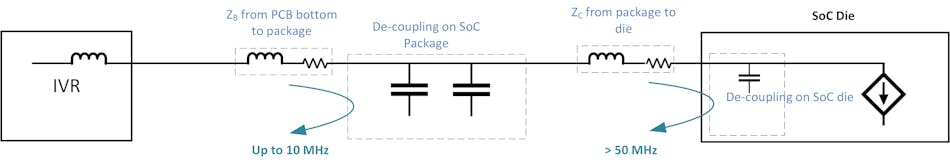

图 7 中修订后的 PDN 说明了高带宽 IVR 及其垂直传输布局的综合效果。最显着的区别是批量移除了大容量电容器,并且从稳压器输出到先前要求的去耦电容器的阻抗。

图7. 将 IVR 直接放置在 SoC 下方,可大大降低稳压器和负载之间的 PDN。

图7. 将 IVR 直接放置在 SoC 下方,可大大降低稳压器和负载之间的 PDN。由于带宽较高,IVR 和 SoC 之间的路径上需要的电容器要少得多,以满足 PDN 的目标阻抗。使用 1 个 2.2 μF 0402 电容器、2 个 1 μF 0201 和 3 个 EC1001 215 nF ECAP 形成图 8 所示的 PDN。

图8. EP7123 IVR 的 PDN 阻抗在非常宽的频率范围内是平坦的。

图8. EP7123 IVR 的 PDN 阻抗在非常宽的频率范围内是平坦的。采用 EP7123 等高频 IVR,与前一个示例相同的目标阻抗得到满足,但电容降低了 100 倍,面积减小了 12 倍。由于减少了 BOM 数量,从而节省了成本,并缩小了 PCB 上电源电路的解决方案尺寸。

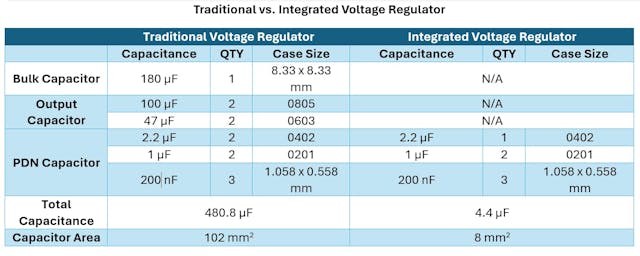

用于 IVR 和传统稳压器的电容器可在表中找到。IVR 需要的电容器要少得多,而且需要的电容器尺寸更小。高带宽调节允许移除用于传统稳压器的大大容量电容器,将改进 PDN 所需的电容器限制为仅几个 0402 和 0201 电容器,以满足目标阻抗。这有助于降低 PCB 复杂性、解决方案尺寸、BOM 数量,从而降低设计的最终成本。

传统稳压器和 IVR 之间的输出电容器和 PDN 电容器的比较表明,IVR 的输出阻抗可以用更少的电容器进行补偿。

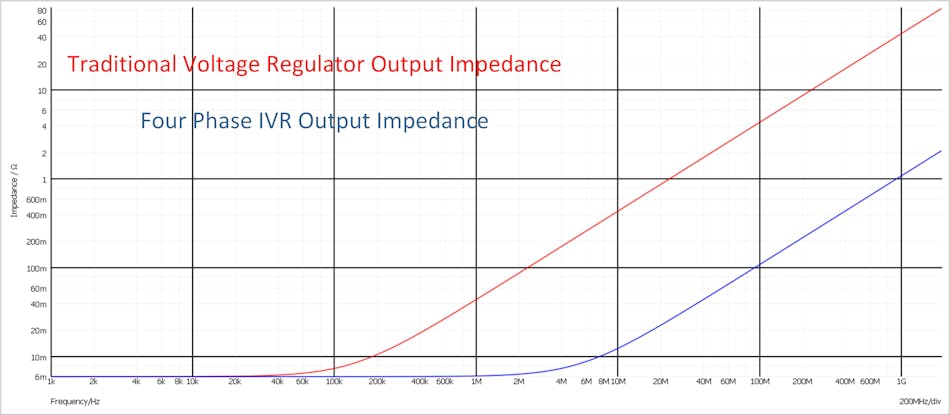

除了减少所需电容器的数量外,与图 9 所示的传统稳压器 (40 kHz) 相比,IVR 阻抗在更宽的频率范围 (2 MHz) 内也更平坦、更一致,没有可能导致不稳定行为的不需要的谐振。这些谐振可能会导致电源不稳定;在可能的情况下能够减少它们是理想的。总体而言,使用 EP7123 等 IVR 可以使电源的行为更加可预测,同时还可以实现更简单的设计。

图9. IVR 和传统稳压器之间的 PDN 比较表明,在更宽的频率范围内,IVR 的阻抗更平坦。

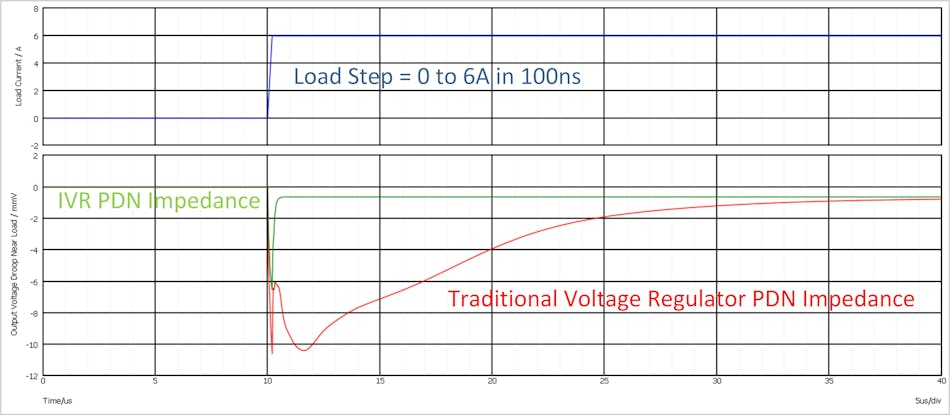

图9. IVR 和传统稳压器之间的 PDN 比较表明,在更宽的频率范围内,IVR 的阻抗更平坦。图 10 所示的瞬态性能清楚地证明了具有更平坦的阻抗曲线随频率变化的好处。仿真将稳压器建模为简单的输出阻抗模型。因此,它仅用于比较传统调节器与 IVR 之间下垂的相对差异。

Empower 半导体

图10. IVR 的负载瞬态响应要快得多,并且会导致输出电压下的下降更低。

图10. IVR 的负载瞬态响应要快得多,并且会导致输出电压下的下降更低。IVR 的较低输出电感导致对负载阶跃的响应更快,输出电压的下降更低。较低的输出电压下降使工程师能够将输出电压设置得更低,同时仍能满足其系统的最低输出电压要求。这降低了 SoC 的静态功耗,并允许为最大允许电压留出更大的余量。

凭借超快恢复(<1 μs 对 >15 μs),SoC 可以避免时钟缩放或时钟扩展等缓解策略,并充分发挥其潜力。平坦的频率响应还消除了不需要的谐振,从而产生更清晰的瞬态响应,没有感应尖峰。总体而言,与传统稳压器设计相比,高频 IVR 可实现更简单的设计和更高的性能。

使用 IVR 优化 Power-Deliver 网络

在现代电子产品中,FPGA、SoC 和 CPU 等负载需要具有低阻抗和平坦频率响应的 PDN,以便稳压器能够充分地为动态负载供电。传统的稳压器需要许多大容量电容器、旁路电容器和本地高频电容器,以补偿稳压器的较高输出阻抗(高输出阻抗)、PCB 中的寄生电感和电容器的 ESL。

尽管添加了所有电容器来改善 PDN,但仍可能发生不需要的谐振,从而导致电源振荡,并且无法避免缓慢恢复到动态负载阶跃。

高频 IVR(如 Empower Semiconductor 的 EP7123)可用于优化 PDN 以消除不需要的振荡。IVR 通常可以直接放置在负载下方,这简化了 PDN 并减少了 PCB 走线和过孔的功率损耗。IVR 集成了输入和输出电容器,从而减少了 PCB 上的元件数量。

与传统稳压器相比,更高的开关频率可在更宽的带宽上提供低阻抗,从而大大减少 PCB 上需要的输出电容器。这允许在频率范围内实现更平坦的输出阻抗(没有不需要的峰值和谷值)。

垂直供电可减少 PCB 层数,从而降低 PCB 复杂性。在负载下放置有助于释放顶层的 PCB 空间,这些空间可用于放置无法放置在底层的内存或其他元件。

总体而言,IVR 使设计人员能够显著提高电源完整性,同时减少组件数量。

售前咨询专员

售前咨询专员